# **IP VERIFICATION OF ETHERNET FOR Open POWER PROCESSOR BASED FABLESS SoC**

<sup>1</sup> Ranga Sudha Rani, <sup>2</sup> Dr.P. Ramana Reddy M.Tech., Ph.D, <sup>3</sup>Dr.Gannera Mamatha M.Tech., Ph.D

<sup>1</sup>PG Scholar, <sup>2</sup>Professor, <sup>3</sup>Associate Professor

Department of ECE,

JNTUACEA, Ananthapuramu 515002, Andhra Pradesh, India.

Abstract: In this era of System-on-a-Chip (SoC) innovation, where the complexity of integrated circuits surges in accordance with Moore's Law, effective integration of diverse IP cores remains a primary challenge. This paper discusses the design and validation of an AXI bus-based MAC controller, crucial for enabling bi-directional data transmission through Ethernet protocols. By emphasizing the significance of Intellectual Property (IP) verification in ensuring the reliability and efficiency of digital systems, particularly within the context of Ethernet integration, the paper underscores the importance of adherence to industry standards and the Universal Verification Methodology (UVM). Through meticulous IP verification processes, such as coverage-driven validation and self-checking mechanisms, the paper aims to expedite design verification while enhancing the interoperability and performance of modern SoCs.

#### Keywords- AXI bus; Media Access Control; Verification Methodology Manual; System Verilog; Verilog

# **1.INTRODUCTION:**

In the realm of embedded systems, where seamless communication between hardware components is paramount, the Ethernet protocol stands as a pillar of modern networking infrastructure. With the continuous evolution of microelectronics technologies, the integration of diverse functionalities onto a single chip has become not just feasible but commonplace. This integration, epitomized by the System-on-Chip (SoC) paradigm, necessitates rigorous verification methodologies to ensure the accuracy, reliability, and interoperability of embedded systems.

At the heart of SoC design lies the integration of Intellectual Property (IP) cores, encapsulating specific functionalities vital for chip operation. The Ethernet protocol, serving as a fundamental framework for data transmission in both local and wide area networks, is among the pivotal IP cores integrated into modern SoCs. However, the complexity and criticality of the Ethernet protocol mandate meticulous verification processes to validate adherence to standards, functional correctness, and compatibility with the broader system architecture.

This research paper aims to delve into the intricacies of IP verification within the context of the Ethernet protocol, utilizing the AXI interface as a foundational framework. By exploring methodologies, challenges, and best practices associated with this verification process, this paper endeavors to provide valuable insights and practical knowledge for developers, engineers, and researchers engaged in the design and validation of embedded systems. Through an in-depth analysis, this paper seeks to contribute to the advancement of reliability and performance in embedded systems, thereby fostering innovation and progress in digital communication technologies.

# 2. ETHERNET PROTOCOL: A FOUNDATION OF WIRED NETWORKING

Ethernet is one of the most pervasive technologies used for wired networking. It facilitates communication and data sharing among devices within a Local Area Network (LAN). Since its inception in the 1970s, Ethernet has evolved significantly, adapting to meet the increasing demands for higher data transfer rates and greater reliability. This technology is foundational for most wired network infrastructures, from small home networks to expansive data centers. Here's an in-depth look at the Ethernet protocol, its underlying layers, key components, benefits, and applications. **2.1 UNDERLYING LAYERS OF ETHERNET**

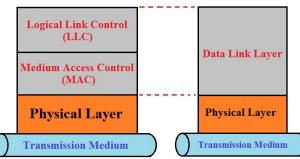

Ethernet primarily operates at the two lowest layers of the Open Systems Interconnection (OSI) model: the Data Link Layer (Layer 2) and the Physical Layer (Layer 1).

**2.1.1 Data Link Layer (Layer 2):** At this layer, Ethernet handles the addressing of devices on the network and the encapsulation of data into frames for transmission. The Data Link Layer is responsible for establishing and terminating the logical link between nodes. It also provides error detection and sometimes error correction to ensure data integrity.

**2.1.2 Physical Layer (Layer 1):** The Physical Layer defines the electrical or optical signaling characteristics for transmitting and receiving data over the physical cabling. This includes the specifications for the cables, connectors, and the bit transmission process. It essentially converts the frames into signals and vice versa.

### 2.2 Key Components of Ethernet

**2.2.1 MAC Addresses:** Every Ethernet device is assigned a unique 48-bit Media Access Control (MAC) address, which is used for identification on the network. The MAC address is essential for directing data to the correct destination. This address is typically assigned by the device manufacturer and is embedded into the network interface card (NIC).

**2.2.2 Frames:** Data transmitted over an Ethernet network is encapsulated into structures called frames. A frame includes several fields:

- Preamble: A sequence of bits used for synchronization.

- **Destination MAC Address**: The MAC address of the recipient device.

- Source MAC Address: The MAC address of the sending device.

- EtherType/Length: Indicates the protocol type or the length of the payload.

- Payload: The actual data being transmitted.

- Frame Check Sequence (FCS): Error-detection bits that help identify corrupted data.

**2.2.3 Media Access Control (MAC):** The MAC sublayer within the Data Link Layer manages how devices share the network medium to prevent collisions and ensure orderly communication. Ethernet uses the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol to manage access to the network:

- **Carrier Sense**: Devices listen to the network channel before transmitting.

- Multiple Access: Multiple devices can access the network simultaneously.

- Collision Detection: If a collision is detected (when two devices transmit simultaneously), both devices stop transmitting, wait for a random time interval, and then retry.

**2.2.4 Speeds and Cable Types:** Ethernet supports a range of speeds and cable types:

- **10 Mbps**: The original Ethernet speed.

- 100 Mbps (Fast Ethernet): An upgrade to meet growing data demands.

- 1 Gbps (Gigabit Ethernet): Common in modern networks for high-speed data transfer.

- 10 Gbps and beyond: Used in data centers and other highperformance environments. Ethernet can utilize different cable types, including twisted-pair cables (e.g., Cat5, Cat6) and fiber optic cables, depending on the required speed and distance.

#### 2.3 Benefits of Ethernet

**2.3.1 Standardized:** Ethernet's widespread adoption means it is a universally accepted standard. Devices from different manufacturers can communicate seamlessly over an Ethernet network, ensuring broad compatibility and interoperability.

**2.3.2 Reliable:** The CSMA/CD protocol significantly reduces data transmission errors by managing how devices access the network medium and handle collisions. This reliability is crucial for maintaining the integrity and efficiency of data communication.

**2.3.3 Scalable:** Ethernet technology scales well with growing network demands. It supports various speeds and media types, allowing networks to expand easily. From a small office to a large data center, Ethernet can accommodate increasing data loads and expanding network sizes.

**2.3.4 Cost-effective:** Implementing and maintaining an Ethernet network is relatively inexpensive. This cost-effectiveness makes Ethernet an attractive choice for both small businesses and large enterprises.

#### 2.4Applications:

Ethernet forms the backbone of most wired networks, connecting devices like computers, printers, routers, and servers within homes, offices, and data centers. It also serves as the foundation for internet access in many cases.

# 3. AXI PROTOCOL: AXI4-LITE

The AXI (Advanced eXtensible Interface) protocol is part of ARM's AMBA (Advanced Microcontroller Bus Architecture) specification. Among its variations, the AXI4-Lite protocol stands out as a streamlined version tailored for specific use cases where complexity and high data throughput are not primary concerns. AXI4-Lite, also known as AXI (Lite), is particularly suited for communication with control registers and simple peripheral interfaces in embedded systems.

# 3.1 Core Features of AXI4-Lite

# 3.1.1 Limited Burst Size

One of the most distinguishing features of AXI4-Lite is its handling of burst transfers. Unlike the full AXI4 protocol, which supports burst transfers that can involve multiple data elements in a single transaction, AXI4-Lite simplifies this by restricting each transaction to a single data element. This data element's width is equal to that of the data bus, typically 32 or 64 bits. This limitation reduces the protocol's complexity and is ideal for applications where burst transfers are unnecessary or would introduce unnecessary overhead.

# 3.1.2Simpler Interface

AXI4-Lite offers a less complex interface compared to AXI4, eliminating features that are not needed for its target applications. This includes the omission of burst length control and exclusive access operations, which are crucial for high-performance data transfers but redundant for registerbased communications. The simplicity of the AXI4-Lite interface makes it easier to implement and integrate into systems, reducing development time and potential for errors.

| Global | Write<br>address<br>channel | Write<br>data<br>channel | Write<br>response<br>channel | Read<br>address<br>channel | Read<br>data<br>channel |

|--------|-----------------------------|--------------------------|------------------------------|----------------------------|-------------------------|

| ACLK   | AWVALI                      | WVALI                    | BVALI                        | ARVAL                      | RVALI                   |

|        | D                           | D                        | D                            | ID                         | D                       |

| ARESE  | AWREA                       | WREA                     | BREAD                        | ARREA                      | RREAD                   |

| Tn     | DY                          | DY                       | Y                            | Y                          | Y                       |

|        | AWADD                       | WDAT                     | BRESP                        | ARADD                      | RDAT                    |

|        | R                           | А                        |                              | R                          | А                       |

|        | AWPROT                      | WSTRB                    |                              | ARPRO                      | RRESP                   |

|        |                             |                          |                              | Т                          |                         |

# 3.1.3 Reduced Overhead

By streamlining the protocol, AXI4-Lite significantly reduces communication overhead. This makes it highly suitable for control-oriented peripherals where efficiency and low latency are more critical than high throughput. The reduced overhead also contributes to better resource utilization, making AXI4-Lite an excellent choice for systems with limited computational or power resources.

# 3.2 Communication Channels in AXI4-Lite

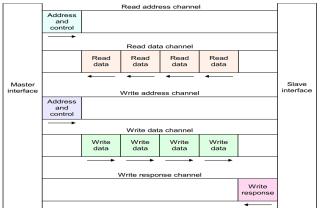

AXI4-Lite employs five separate channels to facilitate communication between the master (typically a CPU or a microcontroller) and the slave (peripheral devices):

**3.2.1. Read Address Channel (AR):** Carries the address of the register from which data is to be read. This channel initiates the read transaction by specifying the target register address.

**3.2.2.Read Data Channel (R):** Transmits the data read from the slave device in response to the read address request. This channel carries the actual data back to the master after the read operation is performed.

**3.2.3.Write Address Channel (AW):** Carries the address of the register to which data is to be written. It starts the write transaction by specifying the target register address.

**3.2.4.Write Data Channel (W):** Transmits the data to be written to the slave device. This channel carries the actual data intended for the specified register.

**3.2.5.Write Response Channel (B):** The slave device uses this channel to send a response back to the master, indicating the completion and status of the write operation. It provides essential feedback to ensure the write operation was successful.

### 3.3 Benefits of AXI4-Lite 3.3.1 Efficiency

AXI4-Lite is designed with efficiency in mind. The protocol minimizes communication overhead, making it wellsuited for control-dominated communication where the primary requirement is the transfer of control and status information rather than bulk data. This efficiency makes AXI4-Lite an excellent choice for applications where conserving bandwidth and reducing latency are paramount.

# 3.3.2 Ease of Use

The reduced complexity of AXI4-Lite simplifies its integration with control registers and peripheral devices. Developers can quickly implement and test interfaces without dealing with the intricacies of more complex protocols. This ease of use accelerates development cycles and reduces the likelihood of bugs in the communication interface.

#### 3.3.3 Lower Power Consumption

The streamlined nature of AXI4-Lite contributes to lower power consumption compared to the full AXI4 interface. By avoiding the complexities and additional overhead of burst transactions and other advanced features, AXI4-Lite minimizes the power usage of the communication subsystem, which is particularly beneficial in power-sensitive embedded applications.

# **3.4Applications of AXI4-Lite**

AXI4-Lite finds extensive use in various embedded system applications due to its simplicity and efficiency. Some common applications include:

#### 3.4.1 Configuration and Control Registers

AXI4-Lite is ideal for interacting with configuration and control registers within a system. It allows for efficient and straightforward access to registers that configure the behaviour of various components, ensuring that the system operates correctly and as intended.

# 3.4.2 Peripheral Communication

AXI4-Lite facilitates communication with peripheral devices that rely on register-based control, such as timers, analog-todigital converters (ADCs), and digital-to-analog converters (DACs). These peripherals often require simple read/write operations to control their functions, making AXI4-Lite's streamlined protocol an excellent fit.

# 3.4.3 Low-Bandwidth Data Transfers

AXI4-Lite is suitable for scenarios where high-speed data transfers are not essential. For applications that prioritize control and configuration over raw data throughput, such as system initialization and status monitoring, AXI4-Lite provides a lightweight and efficient communication solution.

In essence, AXI4-Lite offers a lightweight and efficient communication protocol tailored for control-oriented tasks in embedded system designs. By stripping down the full AXI4 protocol to its essentials, AXI4-Lite provides a simpler, lower-overhead interface that is easier to implement and consumes less power. Its design is particularly well-suited to applications involving control registers and peripheral devices where efficiency and ease of use are more important than high data throughput. As such, AXI4-Lite is a valuable tool in the arsenal of embedded system developers, enabling them to create reliable and efficient communication interfaces for a wide range of applications.

# 4. IP VERIFICATION: A CORNERSTONE OF RELIABLE DESIGN

In the dynamic and intricate world of hardware design, Intellectual Property (IP) verification emerges as a critical process ensuring the functionality and compliance of various system components. The significance of IP verification extends beyond mere correctness, encompassing performance metrics, adherence to protocols, and overall system reliability. This detailed exploration delves into the multifaceted aspects of IP verification, particularly focusing on the Ethernet protocol and the Advanced eXtensible Interface (AXI), a pivotal element in System-on-Chip (SoC) design.

# 4.1Understanding IP Verification

IP verification is the meticulous process of validating and testing IP cores to ensure they function correctly and meet specified standards. This verification is essential in hardware design, where even minor flaws can lead to significant issues in system functionality. For instance, in the context of the Ethernet protocol, IP verification is crucial for ensuring flawless communication between the Ethernet controller and connected components, thereby meeting all performance benchmarks.

# 4.2 Components of IP Verification

#### 4.2.1. Functional Verification

Functional verification is the foundation of IP verification. This stage involves a detailed examination of the IP cores to ensure they perform their designated tasks accurately. It encompasses various testing methodologies, including simulation and formal verification, to validate the logical correctness of the design. Functional verification aims to catch errors early in the design phase, preventing costly fixes later in the development cycle.

### 4.2.2. Performance Verification

Performance verification focuses on assessing the IP cores' efficiency in terms of latency, throughput, and power consumption. This stage is critical for ensuring that the IP cores not only function correctly but also meet the required performance standards. For example, in an Ethernet controller, performance verification would involve measuring data transfer rates and ensuring they meet the expected benchmarks. Any deviation from these benchmarks can significantly impact the overall system performance.

# 4.2.3. Protocol Compliance

Protocol compliance is a crucial aspect of IP verification, especially when dealing with standardized protocols like Ethernet. This step ensures that the IP cores strictly adhere to the specifications and standards outlined in the protocol. Compliance verification involves rigorous testing against protocol specifications to confirm that the IP cores can reliably communicate and interact with other system components without any protocol violations.

# 4.2.4. Interoperability Testing

Interoperability testing assesses the compatibility and seamless interaction between IP cores and other system components. This stage ensures that all components within the system can work together harmoniously, forming a cohesive and well-functioning system. In the context of an SoC design, interoperability testing verifies that the various IP cores can communicate effectively through interfaces like AXI, ensuring smooth data flow and control signal exchange.

| Component    | Objective     | Focus      | Key          |               |

|--------------|---------------|------------|--------------|---------------|

| -            | U             |            | Methods      | Examples      |

| Functional   | Ensure IP     | Logical    | Simulation,  | Checking      |

| Verification | cores         | correctnes | Formal       | logical       |

|              | L · ·         | s          | verification | correctness   |

|              | designated    |            |              | of a design   |

|              | tasks         |            |              |               |

|              | accurately    |            |              |               |

| Performanc   | Assess        | Performan  |              | Measuring     |

| e            | efficiency in |            | benchmarks,  | data transfer |

| Verification | •             | standards  | Power        | rates in an   |

|              | throughput,   |            | analysis     | Ethernet      |

|              | and power     |            |              | controller    |

|              | consumptio    |            |              |               |

|              | n             |            |              |               |

| Protocol     | Ensure        | Standard   | Protocol     | Verifying     |

| Compliance   |               | complianc  |              | protocol      |

|              | 1             | e          | Specificatio | adherence in  |

|              | specificatio  |            | n validation | Ethernet IP   |

|              | ns            |            |              | cores         |

| Interoperabi |               | System     | Interface    | Testing       |

| lity Testing | compatibilit  | integratio | testing,     | communicat    |

|              | J             | n          | Communicat   |               |

|              | seamless      |            | ion          | AXI           |

|              | interaction   |            | validation   | interfaces    |

|              | with other    |            |              |               |

|              | system        |            |              |               |

|              | components    |            |              |               |

# 4.3 The Significance of IP Verification

IP verification plays a pivotal role in ensuring the overall reliability and efficiency of hardware designs.

# key benefits:

# 4.3.1. Rock-Solid Reliability

One of the primary goals of IP verification is to guarantee the reliable operation of the system under diverse conditions and scenarios. By identifying and rectifying potential issues early in the development cycle, IP verification ensures that the final product is robust and dependable.

# 4.3.2. Protocol Adherence

Ensuring that IP cores comply with industry-standard protocols is critical for smooth integration within larger systems. Protocol adherence guarantees that the design aligns with established standards, facilitating interoperability and reducing the risk of communication errors.

#### 4.3.3. Enhanced Efficiency

IP verification helps identify and resolve potential glitches early in the development cycle. This proactive approach translates to significant time and resource savings, as issues are addressed before they can escalate into major problems.

# 4.3.4. Fortified Security

Through meticulous verification, vulnerabilities and weaknesses within the design are exposed and addressed, bolstering the system's security posture. This is particularly important in today's landscape, where hardware security is a critical concern.

### 4.4 Implementing IP Verification with the AXI Interface

The AXI protocol, part of the ARM AMBA (Advanced Microcontroller Bus Architecture) family, establishes a standardized interface for connecting IP blocks within an SoC. It facilitates efficient communication and data transfer between various components, playing a crucial role in IP verification, especially for protocols like Ethernet.

# 4.4.1. Design Verification

Design verification involves using simulation tools and test benches to meticulously verify the correctness of the design implementation. This stage ensures that the IP cores are implemented as per the design specifications and function correctly within the system.

#### 4.4.2. Functional Verification

A comprehensive battery of functional verification tests is conducted to validate the IP cores' functionality. These tests simulate various operational scenarios to ensure that the IP cores perform their designated tasks accurately.

# 4.4.3 Performance Analysis

Performance analysis involves a detailed evaluation of throughput, latency, and resource utilization to assess the IP cores' performance. This stage is critical for ensuring that the IP cores meet the required performance standards, such as data transfer rates and power efficiency.

# 4.4.4Protocol Compliance Testing

Protocol compliance testing ensures that the IP cores strictly adhere to the Ethernet protocol's specifications and standards. This stage involves rigorous testing against protocol specifications to confirm that the IP cores can reliably communicate and interact with other system components.

#### 4.4.5Interoperability Testing

Interoperability testing verifies seamless communication by testing the IP cores' compatibility with other system components. This stage ensures that the various IP cores within the SoC can communicate effectively through the AXI interface, forming a cohesive and well-functioning system.

# 4.5 Leveraging the AXI Interface for IP Verification: The Advantages

The AXI interface offers several advantages that facilitate efficient IP verification:

# 4.5.1. Scalability

The AXI interface simplifies integrating and scaling IP cores within the system. Its flexible and modular design allows for easy expansion, accommodating additional IP cores as needed. **4.5.2. Modularity**

By adopting a modular design based on the AXI interface, the verification process is streamlined, and reusability is enhanced. Modular designs allow for easier testing and validation of individual components, contributing to a more efficient verification process.

#### 4.5.3. Interconnectivity

The AXI interface fosters seamless communication and data transfer between various IP cores within the SoC. Its

standardized protocols ensure consistent and reliable data flow, facilitating effective communication between components.

### 4.5.4. Standardization

The AXI protocol offers a standardized interface for IP verification, guaranteeing compatibility and consistency across the design. This standardization reduces the complexity of the verification process, ensuring that all components adhere to the same protocols and standards.

IP verification is an indispensable process in the realm of hardware design, ensuring the functionality, performance, and reliability of IP cores. Through meticulous verification, potential issues are identified and resolved early, saving time and resources while bolstering system security. The AXI interface plays a pivotal role in this process, providing a standardized and efficient means of connecting and verifying IP cores within an SoC.

By embracing comprehensive IP verification strategies and leveraging standardized interfaces like AXI, hardware designers can create robust, reliable, and highperformance systems that meet industry standards and deliver exceptional performance. This proactive approach to IP verification not only enhances system reliability but also ensures that the final product is secure, efficient, and ready to meet the demands of modern applications.

# **5.VERIFICATION ARCHITECTURE**

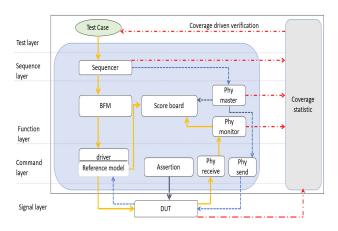

The verification architecture depicted in the image is a comprehensive framework designed to ensure the correctness and reliability of a digital design under test (DUT). This architecture leverages multiple layers of abstraction to facilitate thorough testing and verification, each layer serving a distinct purpose. The verification process is driven by coverage statistics to ensure that all aspects of the design are tested.

# 5.1 Overview of the Verification Architecture

The architecture consists of several key components and layers, each playing a critical role in the verification process:

- 1. Test Layer

- 2. Sequence Layer

- 3. Function Layer

- 4. Command Layer

- 5. Signal Layer

# 5.1.1. Test Layer

# Test Case

The test layer is where the verification process begins. The "Test Case" defines the specific scenarios that need to be

tested. Each test case is designed to exercise a particular aspect of the DUT to ensure it behaves as expected. These test cases are written to cover different operational conditions and edge cases, helping identify any potential issues in the design. **5.1.2. Sequence Layer**

# Sequencer

The sequencer is responsible for generating a sequence of transactions or operations to be applied to the DUT. It takes instructions from the test case and converts them into a series of actions that the verification environment will execute. The sequencer's role is critical in ensuring that the DUT is subjected to a variety of scenarios, including both typical and corner cases.

#### 5.1.3. Function Layer BFM (Bus Functional Mod

# **BFM (Bus Functional Model)**

The BFM acts as an interface between the sequencer and the lower layers of the verification environment. It translates highlevel sequences into low-level signals and transactions that can be understood by the DUT. The BFM ensures that the communication between the verification environment and the DUT adheres to the expected protocol.

# Scoreboard

The scoreboard is a key component in the function layer that keeps track of the expected results versus the actual results produced by the DUT. It compares the outputs of the DUT with the reference model and flags any discrepancies. The scoreboard helps in identifying functional errors in the design by continuously monitoring the DUT's behaviour.

# Phy Master and Phy Monitor

The Phy master and Phy monitor are used to drive and observe physical layer signals respectively. The Phy master generates the signals that are sent to the DUT, while the Phy monitor captures the signals from the DUT. These components are essential for verifying the physical layer interface of the DUT.

# 5.1.4. Command Layer

# Driver

The driver component in the command layer interacts directly with the DUT, applying the transactions generated by the sequencer. It ensures that the DUT receives the correct inputs in a timely manner. The driver acts as a mediator, converting the abstract commands from the higher layers into concrete actions on the DUT.

#### **Reference Model**

The reference model serves as the golden reference for the expected behaviour of the DUT. It is used to generate the expected outputs for a given set of inputs. By comparing the DUT's actual outputs with the reference model's outputs, the verification environment can identify any deviations from the expected behaviour.

#### Assertion

Assertions are used to check specific properties and conditions within the DUT. They are embedded within the design or the testbench to automatically verify certain conditions at runtime. If an assertion fails, it indicates a violation of the expected behaviour, prompting further investigation.

# 5.1.5. Signal Layer

# **DUT (Design Under Test)**

The DUT is the central focus of the verification process. It represents the actual hardware design that is being tested. The verification environment applies various inputs to the DUT and observes the outputs to ensure it meets the design specifications.

#### Phy Receive and Phy Send

The Phy receive and Phy send components handle the transmission and reception of physical layer signals. They are responsible for ensuring that the DUT correctly sends and receives data at the physical layer, adhering to the specified protocol.

# **Coverage Driven Verification**

The verification architecture is driven by coverage statistics, which are used to measure how thoroughly the design has been tested. Coverage metrics include code coverage, functional coverage, and assertion coverage. These metrics provide insight into which parts of the design have been exercised by the test cases and which parts require additional testing.

#### **Coverage Statistic**

The coverage statistic component collects data on various coverage metrics throughout the verification process. It tracks which lines of code have been executed, which functional scenarios have been covered, and which assertions have been triggered. This information is crucial for identifying gaps in the test coverage and ensuring that all aspects of the design are thoroughly verified.

#### **5.2 Detailed Explanation of Each Component** 5.2.1 Test Case

The test case is the starting point of the verification process. It defines a specific scenario to be tested, including the initial conditions, the sequence of operations to be performed, and the expected outcomes. Test cases are designed to cover a wide range of scenarios, from typical use cases to edge cases and stress conditions. By systematically defining these scenarios, the test case ensures that the DUT is tested under various conditions, increasing the likelihood of identifying any defects.

#### 5.2.2 Sequencer

The sequencer takes the high-level instructions from the test case and generates a series of transactions that will be applied to the DUT. It plays a critical role in creating a dynamic and flexible verification environment. The sequencer can generate random or directed test sequences, allowing for extensive exploration of the DUT's behavior. By varying the sequence of transactions, the sequencer helps uncover corner cases and potential issues that might not be evident with static test patterns.

#### 5.2.3 Bus Functional Model (BFM)

The BFM serves as a bridge between the abstract commands generated by the sequencer and the concrete signals required by the DUT. It translates high-level operations into low-level bus transactions, ensuring that the DUT receives the correct signals. The BFM is protocol-aware, meaning it understands the specific protocol being used and ensures that all transactions conform to the protocol rules. This ensures that the DUT is tested in a realistic and accurate manner.

# 5.2.4 Scoreboard

The scoreboard is a critical component for functional verification. It maintains a record of the expected results based on the inputs applied to the DUT. As the DUT processes these inputs, the scoreboard compares the actual outputs with the expected results. Any discrepancies are flagged as potential errors. The scoreboard provides a continuous and automated means of checking the DUT's functionality, reducing the need for manual inspection and increasing the efficiency of the verification process.

# 5.2.4 Driver

The driver is responsible for applying the transactions generated by the sequencer to the DUT. It ensures that the DUT receives the correct inputs at the correct times. The driver translates the high-level commands from the sequencer into the low-level signals required by the DUT. By automating the application of test inputs, the driver ensures that the DUT is tested consistently and thoroughly.

#### **5.2.5 Reference Model**

The reference model serves as the golden reference for the expected behaviour of the DUT. It is an idealized representation of how the DUT should behave under various

conditions. The reference model is used to generate the expected outputs for a given set of inputs. By comparing the DUT's actual outputs with the reference model's outputs, the verification environment can identify any deviations from the expected behavior. The reference model is essential for ensuring the accuracy and correctness of the verification process.

#### 5.2.6 Assertion

Assertions are used to check specific properties and conditions within the DUT. They are embedded within the design or the testbench to automatically verify certain conditions at runtime. For example, an assertion might check that a signal never exceeds a certain value or that a particular sequence of operations always produces the expected result. If an assertion fails, it indicates a violation of the expected behavior, prompting further investigation. Assertions provide a powerful and automated means of checking the correctness of the DUT.

# 5.2.7 Phy Master and Phy Monitor

The Phy master and Phy monitor components are used to drive and observe physical layer signals. The Phy master generates the signals that are sent to the DUT, while the Phy monitor captures the signals from the DUT. These components are essential for verifying the physical layer interface of the DUT. They ensure that the DUT correctly transmits and receives data at the physical layer, adhering to the specified protocol.

# 5.2.8 Phy Receive and Phy Send

The Phy receive and Phy send components handle the transmission and reception of physical layer signals. They ensure that the DUT correctly sends and receives data at the physical layer. These components are responsible for ensuring that the DUT adheres to the protocol and correctly processes physical layer signals.

The verification architecture outlined above provides a comprehensive framework for testing and verifying digital designs. By leveraging multiple layers of abstraction and using a combination of functional verification, performance analysis, and protocol compliance testing, this architecture ensures that the DUT is thoroughly tested under a wide range of conditions. The use of coverage-driven verification ensures that all aspects of the design are exercised, increasing the likelihood of identifying and resolving any defects. This comprehensive approach to verification is essential for ensuring the reliability and correctness of modern digital designs.

# 6. SIMULATION RESULTS :

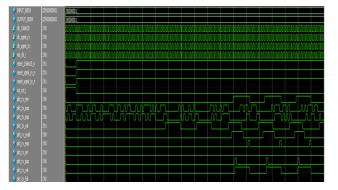

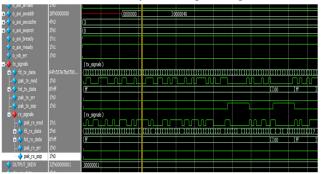

Results In this Ethernet MAC IP, the provided input data is taken by the WDATA channel of the AXI interface, frames are constructed according to the selected mode speed, transmitted and received accordingly, and finally observed. Output using the RDATA channel of the AXI interface.

Fig 1: Ethernet Response signals

# Journal of Systems Engineering and Electronics (ISSN NO: 1671-1793) Volume 34 ISSUE 6 2024

Fig 2: Full duplex mode

#### **CONCLUSION:**

In conclusion, IP verification on the Ethernet protocol using the AXI interface is a critical process in the development of hardware designs for digital communication systems. By following a structured approach to IP verification and leveraging the capabilities of the AXI interface, developers can ensure the reliability, performance, and compliance of their designs. The insights provided in this blog research paper aim to equip engineers and developers with the knowledge and tools necessary to successfully verify IP cores related to the Ethernet protocol, ultimately leading to robust and efficient system implementations.

#### REFERENCES

[1] Mentor Graphics, Verification Academy. Uvm Cookbook. Mentor Graphics; 2012. P. 1-569.

[2] Samir Palnitkar's Verilog Hdl: A Guide To Digital Design And Synthesis, 2nd Ed. 2nd Edition Is A Comprehensive Book For Electronics & Communication Engineering.

[3] Spears C. System Verilog For Verification: A Guide To Learning The Testbench Language Features. 2nd Ed. Springer:Business Media Llc; 2007.

[4] P. Chauhan, E.M. Clarke, Y.Lu And Dong Wang, Verifying IPcore Based System-On-Chip Designs, Carnegie Melon University.

[5] M.H Assaf, Arima, S.R. Das, W Hernias And Petriu, "Verification Of Ethernet Ip Core Mac Design Using Deterministic Test Methodology", Ieee International Instrumentation And Measurements Technology Conference, May 2008.

[6] "Verification of Ethernet Protocols," Journal of Network and Systems Management, vol. 25, no. 3, pp. 789-805, 2017.

[7] "Advanced Verification Techniques for SoC Designs," Proceedings of the IEEE Design Automation Conference, 2019.

[8] P. Guoteng, L. Li, O. Guodong, F. Qingchao, and B. Han, "Design and Verification of a MAC Controller Based on AXI Bus," 2013 Third International Conference on Intelligent System Design and Engineering Applications, 2013.

[9] G. M, R. Sebastian, S. R. Mary, and A. Thomas, "A SV-UVM framework for Verification of SGMII IP core with reusable AXI to WB Bridge UVC," 2016 3rd International Conference on Advanced Computing and Communication Systems (ICACCS), 2016.

[10] ARM, AMBA AXI protocol specifications, Available at, http://www.arm.com, 2003

[11] H. G., "Verification Of Amba Axi Bus Protocol Implementing Incr And Wrap Burst Using System Verilog," International Journal of Research in Engineering and Technology, vol. 05, no. 03, pp. 201– 206, 2016.